Example Designs

The example designs for the Quad SFP28 FMC are hosted on Github.

| Example Designs | |||

|---|---|---|---|

| 10G/25G Ethernet Subsystem Example Design | More info | Git repo | Docs |

10G/25G Ethernet Subsystem based example

Description

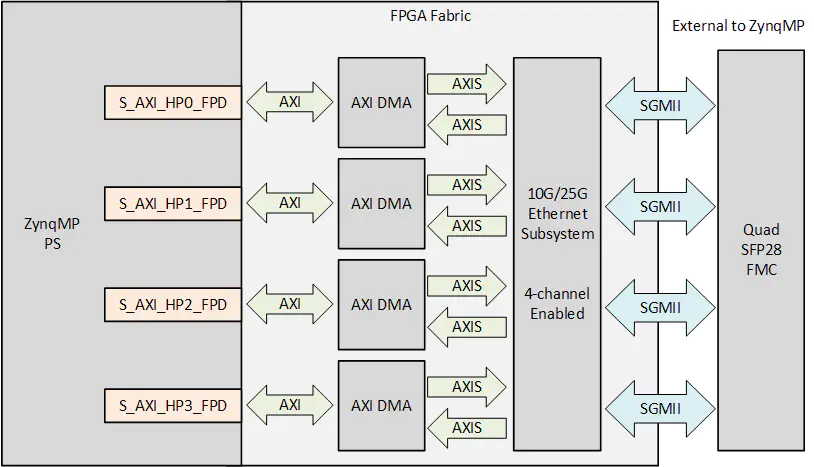

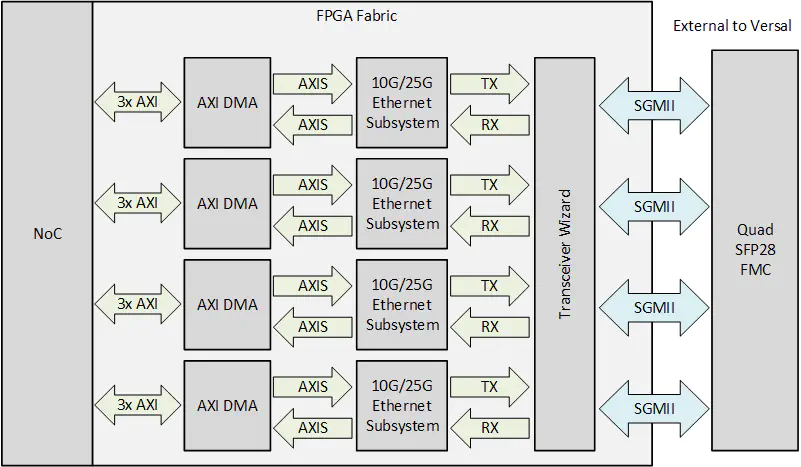

This example design is based on Xilinx’s soft MAC (ie. FPGA implemented), the AMD Xilinx 10G/25G Ethernet Subsystem IP , that can be found in the Vivado IP Catalog. As the MAC is implemented in the FPGA fabric, this example is ideal for pure FPGA designs or Zynq/ZynqMP designs that require some packet processing to be performed in the FPGA.

Links

Block diagrams

Zynq UltraScale+ designs

Versal designs

PS GEM based example

Description

This example design utilizes the Gigabit Ethernet MACs (GEMs) that are embedded into the Processing System (PS) of the Zynq 7000™ and Zynq Ultrascale+™ devices. The embedded MACs used in this example design do not use up any of the FPGA fabric, which makes it ideal for applications that need to use the FPGA for other purposes.

Links

- Coming soon